ODCC超节点大会回顾:奇异摩尔荣获超节点推进计划成员&专家殊荣

发布时间:2026-01-23

发布时间:2026-01-23

信息来源:奇异摩尔微信公众号

字体:

大

中

小

信息来源:奇异摩尔微信公众号

字体:

大

中

小

打印

打印

发布时间:2026-01-23

发布时间:2026-01-23

信息来源:奇异摩尔微信公众号

信息来源:奇异摩尔微信公众号

北京-1月22日,由ODCC(开放数据中心委员会)主办的2026超节点大会在北京顺利举办。本次大会围绕超节点部件、超节点协议、超节点管理、超节点应用四大板块,邀请头部互联网厂商、通信、行业客户、设备制造等行业大咖齐聚北京带来深入产业的一线洞察。奇异摩尔作为ODCC核心成员单位发表主题演讲《超节点协议的需求与挑战:芯粒技术如何加速破局》,提及了超节点系统互联所面临的严峻协议挑战,并系统性地阐释了芯粒技术如何为这一关键瓶颈提供创新性的解决方案与发展路径。

作为对奇异摩尔公司贡献的认可,在本次大会的超节点推进计划发布仪式上,奇异摩尔被正式授予 “超节点推进计划成员单位” 殊荣。同时,公司联合创始人祝俊东受聘担任 “超节点推进计划专家成员” 。这一双重身份标志着奇异摩尔将从组织与实践双重层面,更深入地与超节点应用领域伙伴携手,共同推进高性能超节点基础设施的构建与创新。

奇异摩尔持续积极参与到超节点标准的建设中。2023年开始,奇异摩尔作为最早批生态成员参与到由中国移动主导的OISA1.0协议制定工作中,奠定超节点互联基础。2024年,公司参与由ODCC(开放数据中心委员会)牵头的ETH-X协议制定,并正式加入UALink联盟,持续拓展生态互通性。2025年,公司参与OISA2.0协议制定,全线产品均支持OISA标准,并建立OISA验证平台,着力推动标准落地。同年支持SUE标准,并加入ESUN工作组。

MoE模型训推对

超节点的核心需求与挑战

MoE模型通过稀疏激活连接千亿到万亿级参数专家网络,其路由计算模式导致专家并行依赖于全局All-to-All通信。这要求高速互联的超节点架构支撑数据(Token、激活值、KV-Cache)在各专家GPU间的高频交换,通信带宽与延迟成为系统性能的决定性瓶颈。

带宽需求的刚性增长

在512卡超节点内:互联带宽需求达数百GB/s级,为MoE专家并行的带宽要求。

1024卡及以上大规模集群:带宽需求跃升至TB/s级,成为影响扩展性的关键基础设施瓶颈。

端到端延迟的严苛要求

All-to-All通信占比超过计算周期的 5-10%,即触发系统效率非线性下降的临界点。为维持效率,端到端通信时延需控制在微秒级(<10 μs),对互联架构提出极限挑战。

训练影响:通信耗时高引发尾延迟,导致多数GPU等待少数卡,整体训练迭代时间被拉长,MFU显著降低。

推理影响:首Token延迟对网络RTT极度敏感,逐Token的串行依赖使任何微小网络延迟被放大累积,直接损害用户体验与系统吞吐量。

网络流量与优化路径

MoE动态路由产生海量小数据包,要求网络具备极低的协议开销以避免有效带宽被吞噬。采用量化(如FP8)、稀疏化及压缩技术,可直接减少50%-90%的通信量,是应对此挑战的核心技术方向。

超节点协议的现状和挑战

AI快速演进与硬件标准迭代的“时差”

当前挑战的根源在于 “软节奏”与“硬周期”的错配。AI模型架构(如从Dense模型向MoE专家模型方向探索)与算力需求正以“季度”甚至“月”为单位演进,要求互联协议必须支持近乎线性的万卡级扩展能力。然而,从标准制定、芯片流片到生态成熟的硬件迭代周期,往往以“年”计。这种“时差”导致最先进的AI构想,常受限于当前可用互联技术的天花板,形成发展瓶颈,互联成本高昂。

生态博弈:

私有确定性 vs. 开放灵活性的两难

私有协议之路:以特定厂商技术栈为核心的私有协议,通过芯片与网络的垂直整合,在性能、延迟与确定性达到不错的性能,但生态封闭;用户面临供应商锁定,议价能力减弱,且整个体系的创新步伐完全依赖于单一厂商的技术路线图。

开放协议之路:生态潜力大,厂商共建标准,打破垄断,实现跨品牌设备的互操作性,给予用户更多选择。但生态之间依赖多方深度技术协同,导致短期内多种标准并行的情况仍将持续,碎片化问题难以迅速解决。当前跨厂商、跨集群的互联互通成本居高不下。比如芯片厂商需要为不同的协议设计不同的接口和兼容层,增加芯片开发面积、功耗和研发复杂度。

奇异摩尔在超节点领域的核心优势

针对上述行业痛点,奇异摩尔业内首创通用超节点互联芯粒Kiwi G2G IOD旨在为纷繁复杂的国产AI芯片生态提供了一个统一的 “互联底座” 。通过技术架构革新,芯粒将互联功能专用化,让主算力芯片可专注于计算。

从行业背景看,目前芯粒基础条件已经成熟,主要表现在以下四个方面:

1 英伟达、AMD等多家头部厂商的计算芯片广泛转向芯粒架构;

2 异构集成技术日趋成熟;

3 D2D接口标准化;

4 部分先锋厂商已采用超节点互联芯粒(如Rubin中的NVLink Fusion及Ascend中的Nimbus)。

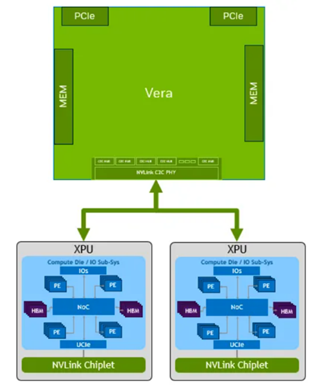

(NVLink融合:xPU通过 NVLink Chiplet访问 NVLink)

随着超节点未来往512-1024卡互联规模演进,相比传统的计算芯片集成IP的方式,超节点互联芯粒有望凭借其和计算完全解耦、灵活配置芯粒数目的物理形态优势,仅使用非先进工艺节点,也能将xPU互联带宽最大提升至2TBbps,超越NVLink 5.0 的1.8TB的带宽性能。(基于UCIe 32Gbps/Lane,Serdes 112Gbps/Lane假设)。

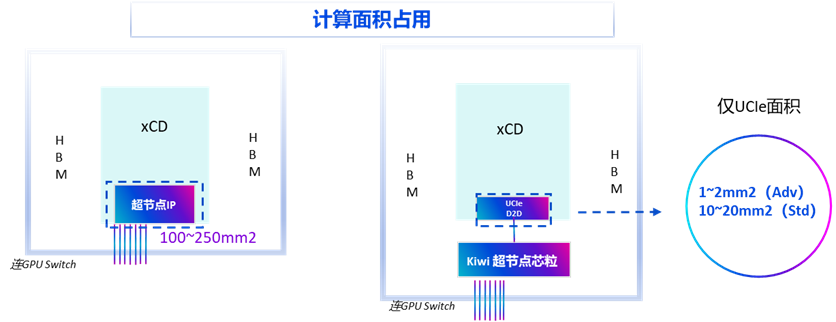

此外,集成超节点IP的方案通常会占用计算Die 20-30%的工艺面积,面对未来参数规模更大、并行计算更复杂的大模型趋势,将宝贵面积留给计算核心已成为下一代xPU芯片的关键设计考量。Kiwi超节点互联芯粒通过和计算Die解耦的方式,占用计算Die的面积仅为1~2mm2(UCIe Adv),10~20mm2(UCIe Std),极大优化计算面积利用率。

(超节点IP vs 超级点互联芯粒计算面积占用)

奇异摩尔持续推进超节点以太链路效率

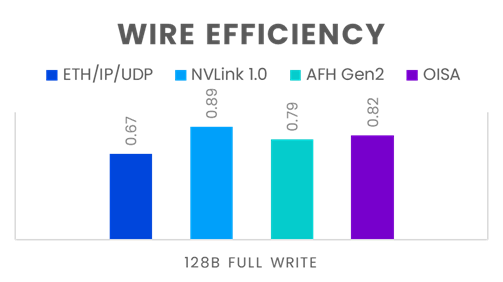

标准的以太网IP/UDP 报头是为异构芯片网络而设计的,然而Scale-up超节点互联使用的是域内同构芯片联接方式,以小包传输占主流流量,所以使用传统标准的以太网IP/UDP报文对于超节点同构网络来说是一种负担。奇异摩尔持续赋能OISA 超节点互联生态,联合生态合作伙伴通过去除MAC以及IP报文头中的冗余字段以及在同构网络中非必须的字段,对Scale-up网络报文头进行了优化, 使其报文传输开销相比标准的ETH/IP/UDP报文封装有显著的提升。

(以太链路效率对比 )

综合而言,超节点芯粒在互联带宽方面扩展性能更优,研发成本更低、研发周期也更短,且具备更强的灵活性,能支持不同的协议包括SUE、OISA、ETH-X,和未来其他主流协议,从而满足不同厂商不同场景的需求,在生态百花齐放的Scale Up系统中支持多协议类型及其升级,从而降低持续研发难度和开发成本。

从当前整个AI产业链发展看,模型的复杂化带来诸多新瓶颈,单纯堆砌硬件已经较难大幅提升训练效率,而硬件面临摩尔定律失效,硬件红利急速衰减的情况,仅依靠原本各环节“单点技术创新”的模式,很难满足AI大模型的训练需求。在此背景下,软硬件全栈协同的新范式成为趋势,其将对算力的实际转化效率、商业落地的成本和速度有极大提升,有效帮助大模型的快速迭代,也是AI产业走向成熟和深化的必由之路。

相关人物